QRコード

お問い合わせ

ファックス

+86-579-87223657

住所

中国浙江省金華市武夷県紫陽街Wangda Road

各半導体製品の製造には数百のプロセスが必要であり、製造プロセス全体が8つのステップに分かれています。ウェーハ処理 - 酸化 - フォトリソグラフィ - エッチング - 薄膜の堆積 - 相互接続 - テスト - パッケージング.

![]()

ステップ1:ウェーハ処理

すべての半導体プロセスは、一粒の砂から始まります!砂に含まれるシリコンは、ウェーハを生産するために必要な原料であるためです。ウェーファーは、シリコン(SI)またはアルセニドガリウム(GAAS)で作られた単結晶シリンダーから切断された丸いスライスです。高純度のシリコン材料を抽出するには、最大95%の二酸化シリコン含有量を備えた特別な材料であるシリカ砂が必要です。これは、ウェーハを作るための主要な原料でもあります。ウェーハ処理は、上記のウェーハを作成するプロセスです。

インゴットキャスティング

まず、一酸化炭素とシリコンを分離するために砂を加熱する必要があり、プロセスは超高純度電子グレードのシリコン(EG-SI)が得られるまで繰り返されます。高純度のシリコンは液体に溶けて、半導体製造の最初のステップである「インゴット」と呼ばれる単結晶固体形態に固まります。

シリコンインゴット(シリコン柱)の製造精度は非常に高く、ナノメートルレベルに達し、広く使用されている製造方法はCzochralskiメソッドです。

インゴット切断

前のステップが完了した後、インゴットの両端をダイヤモンドソーで切り取り、特定の厚さの薄いスライスにカットする必要があります。インゴットスライスの直径は、ウェーハのサイズを決定します。より大きくて薄いウェーハは、より使いやすいユニットに分けることができ、生産コストを削減するのに役立ちます。シリコンインゴットを切断した後、スライスに「フラットエリア」または「デント」マークを追加して、後続のステップで処理方向を標準として設定する必要があります。

ウェーハ表面研磨

上記の切断プロセスで得られたスライスは、「裸のウェーハ」と呼ばれます。つまり、未処理の「生のウェーハ」です。裸のウェーハの表面は不均一であり、回路パターンを直接印刷することはできません。したがって、最初に粉砕および化学エッチングプロセスを介して表面欠陥を除去し、次に磨いて滑らかな表面を形成し、洗浄中に残留汚染物質を除去して、きれいな表面の完成したウェーハを取得する必要があります。

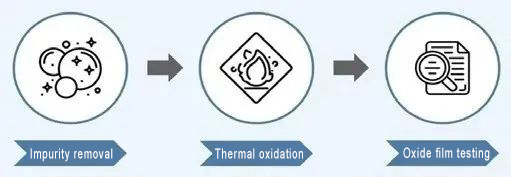

ステップ2:酸化

酸化プロセスの役割は、ウェーハの表面に保護膜を形成することです。ウェーハを化学的不純物から保護し、漏れ電流が回路に入るのを防ぎ、イオン移植中の拡散を防ぎ、エッチング中にウェーハが滑るのを防ぎます。

酸化プロセスの最初のステップは、不純物と汚染物質を除去することです。有機物、金属不純物を除去し、残留水を蒸発させるための4つのステップが必要です。洗浄後、ウェーハは摂氏800〜1200度の高温環境に配置でき、二酸化シリコン(つまり「酸化物」)層は、ウェーハの表面の酸素または蒸気の流れによって形成されます。酸素は酸化物層に拡散し、シリコンと反応してさまざまな厚さの酸化物層を形成し、酸化が完了した後にその厚さを測定できます。

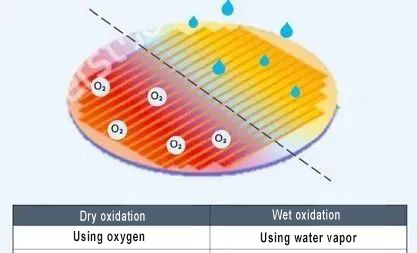

酸化反応の異なる酸化剤に応じて、乾燥酸化と湿潤酸化により、熱酸化プロセスは乾燥酸化と湿潤酸化に分割できます。前者は、純粋な酸素を使用して二酸化シリコン層を生成しますが、これは遅いですが、酸化物層は薄く濃いです。後者には、酸素と非常に溶けやすい水蒸気の両方が必要です。これは、高速成長速度が低密度の比較的厚い保護層によって特徴付けられます。

酸化剤に加えて、二酸化シリコン層の厚さに影響する他の変数があります。第一に、ウェーハ構造、その表面欠陥、内部ドーピング濃度は、酸化物層の生成速度に影響します。さらに、酸化装置によって生成される圧力と温度が高いほど、酸化物層が速く生成されます。酸化プロセス中に、ウエーハを保護し、酸化度の違いを減らすために、ユニットのウェーハの位置に応じてダミーシートを使用する必要があります。

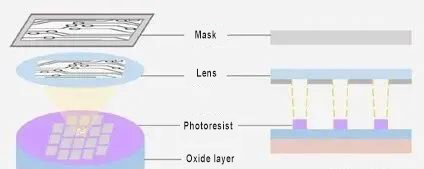

ステップ3:フォトリソグラフィ

フォトリソグラフィは、光を介してウェーハに回路パターンを「印刷」することです。ウェーハの表面にある半導体製造に必要な飛行機マップを描くことができると理解できます。回路パターンの細かさが高いほど、完成したチップの統合が高く、これは高度なフォトリソグラフィテクノロジーを通じて達成する必要があります。具体的には、フォトリソグラフィは、フォトレジスト、露出、発達のコーティングの3つのステップに分けることができます。

コーティング

ウェーハに回路を描く最初のステップは、酸化物層にフォトレジストをコーティングすることです。 Photoresistは、化学的性質を変更することにより、ウェーハを「写真用紙」にします。ウェーハの表面のフォトレジスト層が薄くなるほど、コーティングが均一になり、印刷できるパターンが細かくなります。この手順は、「スピンコーティング」メソッドで実行できます。光(紫外線)反応性の違いによれば、フォトレジストは、正と負の2つのタイプに分けることができます。前者は、光にさらされた後に分解して消え、暴露された領域のパターンを残し、後者は光にさらされた後に重合し、露出した部分のパターンを現れます。

暴露

ウェーハでフォトレジストフィルムが覆われた後、回路印刷は光の露出を制御することで完了することができます。このプロセスは「露出」と呼ばれます。露出機器を選択的に通過させることができます。ライトが回路パターンを含むマスクを通過すると、以下のフォトレジストフィルムでコーティングされたウェーハに回路を印刷できます。

露出プロセス中に、印刷されたパターンが細かくなるほど、最終チップが収容できるコンポーネントが増え、生産効率を改善し、各コンポーネントのコストを削減できます。この分野では、現在多くの注目を集めている新しい技術はEUVリソグラフィです。 LAM Research Groupは、戦略的パートナーASMLとIMECとの新しいドライフィルムフォトレジストテクノロジーを共同で開発しました。この技術は、解像度(微調整回路幅の重要な要因)を改善することにより、EUVリソグラフィ曝露プロセスの生産性と収量を大幅に改善できます。

発達

露出後のステップは、開発者にウェーハにスプレーすることです。目的は、印刷回路パターンを明らかにできるように、パターンの覆われていない領域のフォトレジストを除去することです。開発が完了したら、回路図の品質を確保するために、さまざまな測定機器と光学顕微鏡で確認する必要があります。

ステップ4:エッチング

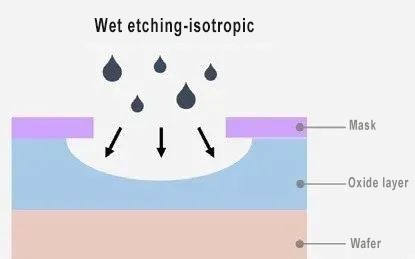

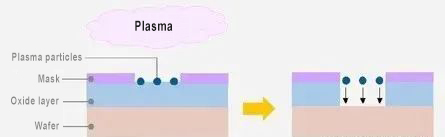

回路図のフォトリソグラフィがウェーハで完成した後、エッチングプロセスを使用して、余分な酸化物膜を除去し、半導体回路図のみを残します。これを行うために、選択した余分な部分を除去するために液体、ガス、またはプラズマを使用します。使用される物質に応じて、エッチングには2つの主要な方法があります。特定の化学溶液を使用して化学的に反応して酸化物膜を除去することと、ガスまたは血漿を使用した乾燥エッチングです。

ウェットエッチング

化学溶液を使用して酸化物膜を除去するウェットエッチングは、低コスト、高速エッチング速度、生産性の高い利点があります。ただし、ウェットエッチングは等方性です。つまり、その速度はどの方向でも同じです。これにより、マスク(または敏感なフィルム)がエッチングされた酸化フィルムと完全に整合しないようにするため、非常に細かい回路図を処理することは困難です。

ドライエッチング

ドライエッチングは、3つの異なるタイプに分割できます。 1つ目は、エッチングガス(主にフッ化水素)を使用する化学エッチングです。ウェットエッチングのように、この方法は等方性です。つまり、細かいエッチングには適していません。

2番目の方法は物理的なスパッタリングです。これは、プラズマのイオンを使用して、過剰な酸化物層に衝撃を与え、除去します。異方性エッチング法として、スパッタリングエッチングは水平方向と垂直方向に異なるエッチング速度を持っているため、その細かさは化学エッチングよりも優れています。ただし、この方法の欠点は、イオン衝突によって引き起こされる物理的反応に完全に依存するため、エッチング速度が遅いことです。

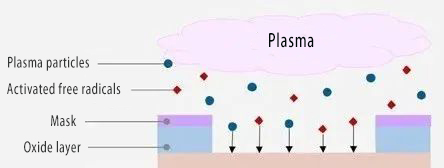

最後の3番目の方法は、反応性イオンエッチング(RIE)です。 RIEは、最初の2つの方法を組み合わせています。つまり、イオン化物理エッチングにプラズマを使用している間、化学エッチングは、血漿活性化後に生成されたフリーラジカルの助けを借りて実行されます。最初の2つの方法を超えるエッチング速度に加えて、RIEはイオンの異方性特性を使用して、高精度パターンエッチングを実現できます。

今日、乾燥エッチングは、細かい半導体回路の収量を改善するために広く使用されています。フルワーファーのエッチングの均一性とエッチング速度の増加を維持することが重要であり、今日の最も高度なドライエッチング機器は、パフォーマンスが高い最も高度なロジックとメモリチップの生産をサポートしています。

Vetek Semiconductorは、プロの中国のメーカーです炭化物コーティング, 炭化シリコンコーティング, 特別なグラファイト, 炭化シリコンセラミックそしてその他の半導体セラミック。 Vetek Semiconductorは、半導体業界向けのさまざまなSICウェーハ製品に高度なソリューションを提供することに取り組んでいます。

上記の製品に興味がある場合は、お気軽に直接お問い合わせください。

暴徒: +86-180 6922 0752

WhatsApp:+86 180 6922 0752

メール:anny@veteksemi.com

+86-579-87223657

中国浙江省金華市武夷県紫陽街Wangda Road

Copyright © 2024 WuYi TianYao Advanced Materials Tech.Co.,Ltd.無断転載を禁じます。

Links | Sitemap | RSS | XML | プライバシーポリシー |